# Module Placement during FPGA Partial Reconfiguration

Jin Hu

September 2<sup>nd</sup>, 2005

#### Outline

#### Previous Work

- Individual Modules

- Modules with Wrappers

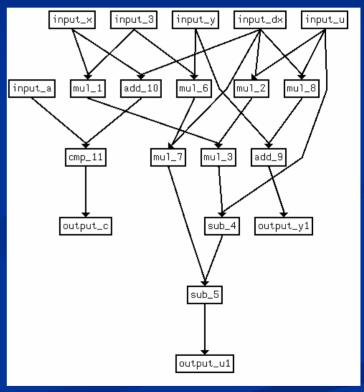

#### Dataflow Graphs

- Overview

- Considerations

#### Experiments

- Unconstrained

- Constrained

- Constrained with Interface

- Full vs. Partial Mapping

#### Future Work

- Reason for Placement Failure

- Systematic Layout

#### Conclusion

FPGA Virtex-4<sup>TM</sup> Board

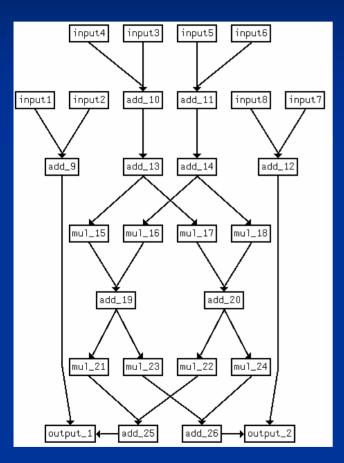

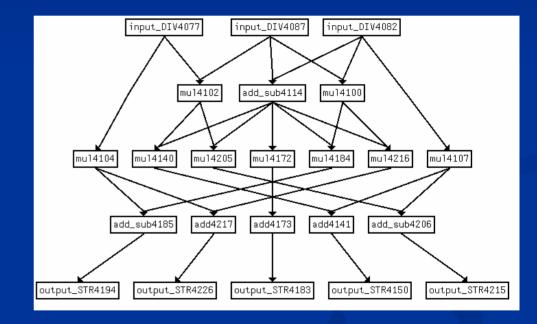

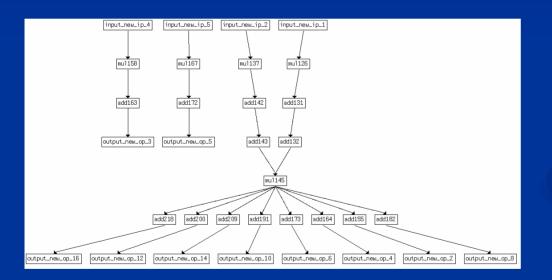

# Dataflow Graphs Overview

Design 1

Design 2

# Dataflow Graphs Considerations

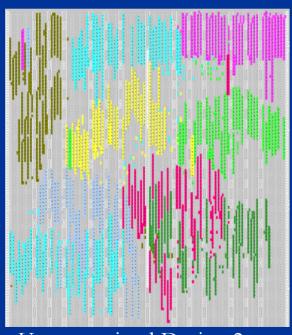

Unconstrained Design 2

Constrained Design 2

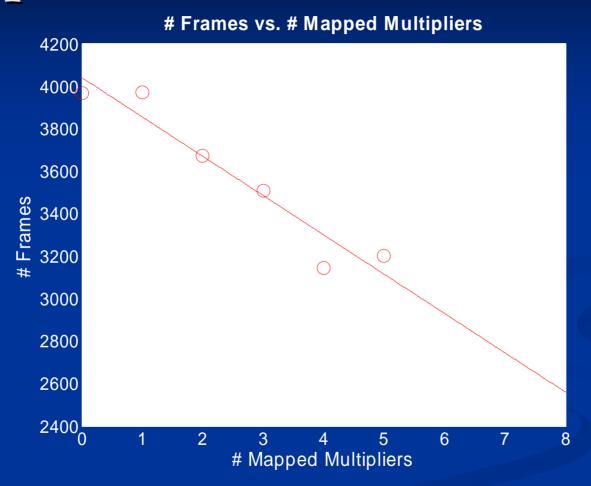

### Experiments – Unconstrained

- Negative correlation between mapping and frames

- Design failed in Cases 6-8

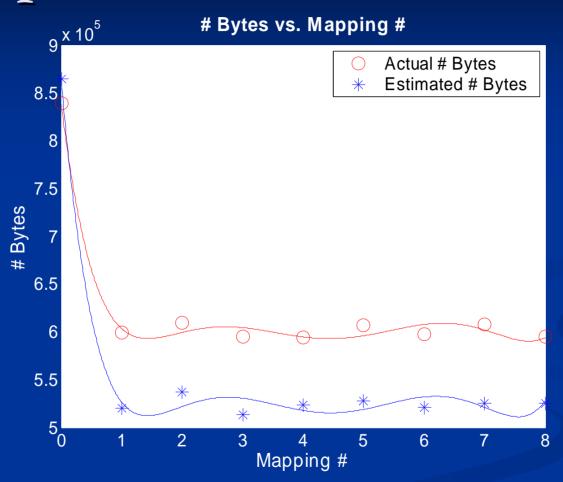

### Experiments – Constrained

- Similar results for different mappings

- Substantial overhead for reconfiguration

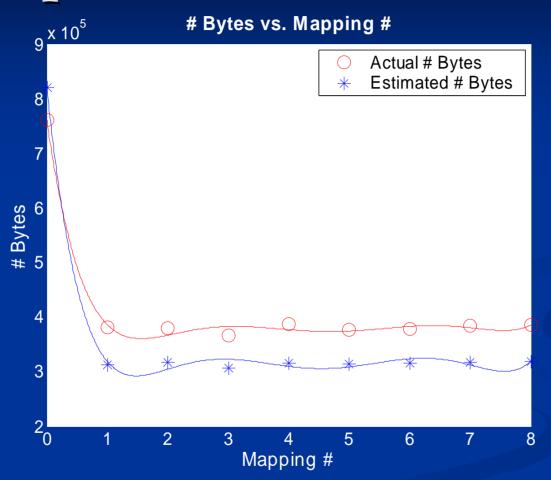

### Experiments – Interface

- Similar results for different mappings

- Fewer bits needed to reconfigure

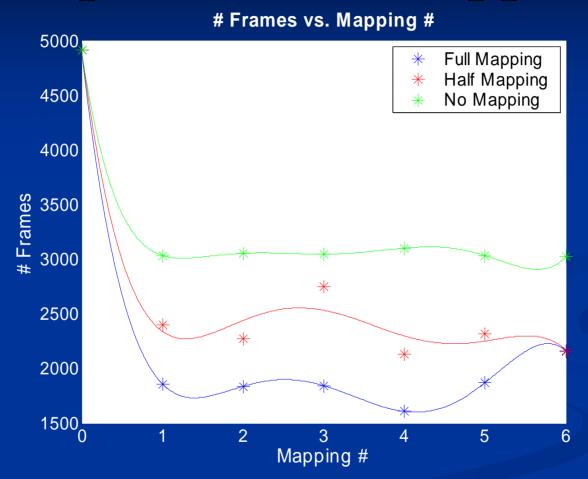

# Experiments - Mapping

Design 3 Design 4

# Experiments – Mapping

- The more mapping involved, the fewer frames needed

- More variation between different mappings

### **Future Work**

- If placement failed, why?

- Congested routing

- Interface issues

- Module Placement

- Systematic Layout

#### Conclusion

Understand building blocks first

Floor planning increases predictability

■ Full mapping most beneficial, if possible

Questions?